## Features

- Power-On Reset Generator with Adjustable Delay Time: 1.25ms to 10s.

- Very Low Quiescent Current: 2.8 $\mu$ A Typical

- High Threshold Accuracy: 0.5% Typ.

- Fixed Threshold Voltages for Standard Voltage Rails from 0.9V to 5V and Adjustable Voltage Down to 0.4V are available.

- Manual Reset (MR) Input.

- Open-Drain RESET Output.

- Temperature Range: -40°C to +125°C

- Package:

SOT23-6L (TPAX3808G01S6)

DFN2x2-6L(TPAX3808G01D6)

## Description

The family of microprocessor supervisory circuits monitor system voltage from 0.4V to 5.0V, asserting an open-drain RESET signal when the SENSE voltage drops below a preset threshold or when the manual reset (MR) pin drops to a logic low. The RESET output remains low for the user-adjustable delay time after the SENSE voltage and manual reset (MR) return above the respective thresholds.

## Applications

- DSP or Microcontroller Applications

- Notebook/Desktop Computers

- FPGA/ASIC Applications

- Portable/Battery-Powered Products

- PDAs/Hand-Held Products

- battery-powered applications.

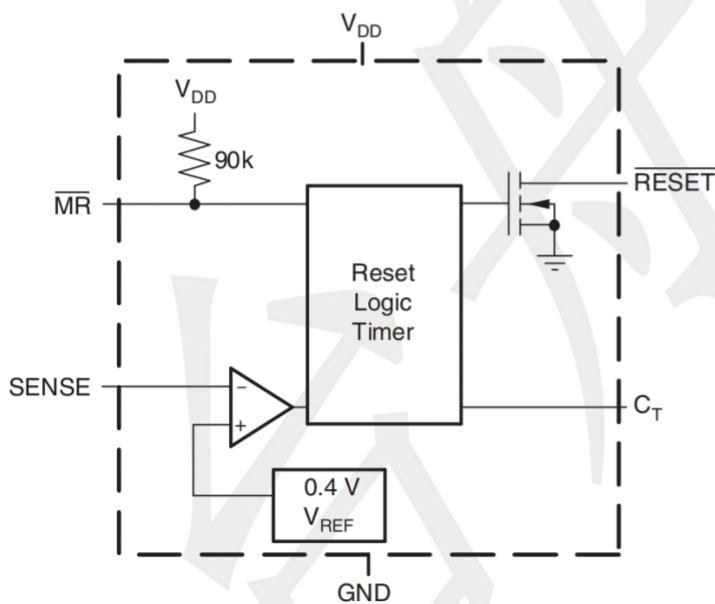

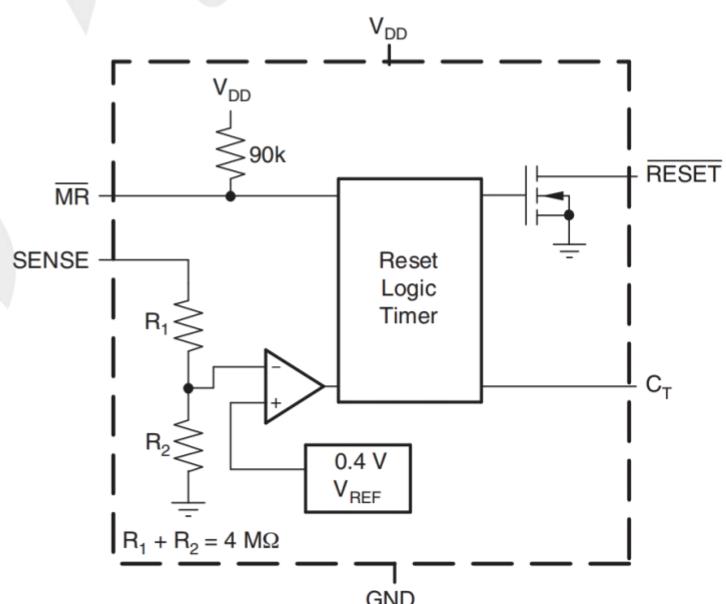

## Block Diagram

Adjustable-Voltage Version

Fixed-Voltage Version

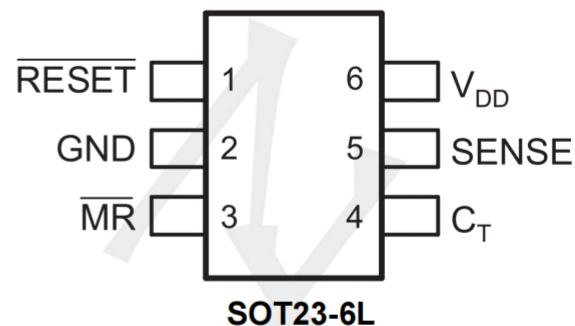

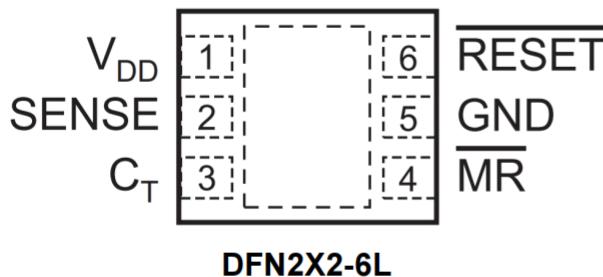

## Pin Definition

## PIN CONFIGURATION

| NAME           | PIN       |           | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------|-----------|-----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | SOT-23-6L | DFN2X2-6L |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| C <sub>T</sub> | 4         | 3         | I   | Reset period programming pin. Connecting this pin to V <sub>DD</sub> through a 40-k $\Omega$ to 200-k $\Omega$ resistor or leaving it open results in fixed delay times (see Electrical Characteristics). Connecting this pin to a ground referenced capacitor $\geq$ 100 pF gives user-programmable delay time. See the Selecting the Reset Delay Time for more information.                                                                                                                              |

| GND            | 2         | 5         | —   | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| MR             | 3         | 4         | I   | Manual reset. Driving this pin low asserts RESET. MR is internally tied to V <sub>DD</sub> by a 90-k $\Omega$ pullup resistor.                                                                                                                                                                                                                                                                                                                                                                             |

| RESET          | 1         | 6         | O   | Reset. This is an open-drain output that is driven to a low impedance state when RESET is asserted (either the SENSE input is lower than the threshold voltage (V <sub>IT</sub> ) or the MR pin is set to a logic low). RESET remains low (asserted) for the reset period after both SENSE is above V <sub>IT</sub> and MR is set to a logic high. A pullup resistor from 10 k $\Omega$ to 1 M $\Omega$ must be used on this pin and allows the reset pin to attain voltages higher than V <sub>DD</sub> . |

| SENSE          | 5         | 2         | I   | Voltage sense. This pin is connected to the voltage to be monitored. If the voltage at this terminal drops below the threshold voltage (V <sub>IT</sub> ), RESET is asserted.                                                                                                                                                                                                                                                                                                                              |

| VDD            | 6         | 1         | I   | Supply voltage. It is good analog design practice to place a 0.1- $\mu$ F ceramic capacitor close to this pin.                                                                                                                                                                                                                                                                                                                                                                                             |

| Thermal Pad    | —         | Pad       | —   | Thermal pad; connect to ground plan to enhance thermal performance of the package.                                                                                                                                                                                                                                                                                                                                                                                                                         |

## Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)

| SYMBOL      | PARAMETER                            | RATINGS              | UNIT |

|-------------|--------------------------------------|----------------------|------|

| $V_{DD}$    | Input Voltage Range                  | -0.3 ~ +7V           | V    |

| $V_{CT}$    | $C_T$ Voltage Range                  | -0.3 ~ $V_{DD}+0.3V$ | V    |

| $V_{RESET}$ | Other Voltage Range                  | -0.3 ~ +7V           | V    |

| $V_{MR}$    | Other Voltage Range                  | -0.3 ~ +7V           | V    |

| $V_{SENSE}$ | Other Voltage Range                  | -0.3 ~ +7V           | V    |

| $I_{RESET}$ | RESET pin Current                    | 5mA                  | mA   |

| $T_J$       | Operating Junction Temperature Range | -40 ~ +125           | °C   |

| $T_{stg}$   | Storage temperature range            | -65 ~ 150            | °C   |

### Note:

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

## Recommended Operation Conditions

| SYMBOL   | PARAMETER                                      | Test Conditions | Min. | Typ. | Max.         | Unit |

|----------|------------------------------------------------|-----------------|------|------|--------------|------|

| $V_{DD}$ | Supply Voltage                                 | --              | 1.7  | --   | 6.5          | V    |

| $V_{IH}$ | Input High Voltage MR                          | --              | --   | --   | $V_{DD}$     | V    |

|          | Input High Voltage for Open-drain RESET, SENSE | --              | 0    | --   | 6.5          | V    |

| $V_{IL}$ | Input Low Voltage MR.                          | --              | --   | --   | $V_{DD}+0.3$ | V    |

| $T_A$    | Operating Temperature                          | --              | -40  | --   | 125          | °C   |

## Electrical Characteristics

Unless otherwise specified,  $-40^{\circ}\text{C} \leq T_A \leq 125^{\circ}\text{C}$ ,  $1.7\text{V} \leq V_{DD} \leq 6.5\text{V}$ ,  $R_{RESET} = 100\text{k}\Omega$ ,  $C_{RESET} = 50\text{pF}$ , Typical values are at  $T_A = +25^{\circ}\text{C}$

| PARAMETER                             |                                         | TEST CONDITIONS                                                    |                                                             | MIN          | TYP       | MAX                | UNIT          |  |

|---------------------------------------|-----------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------|--------------|-----------|--------------------|---------------|--|

| $V_{DD}$                              | Input supply range                      |                                                                    |                                                             | 1.7          |           | 6.5                | V             |  |

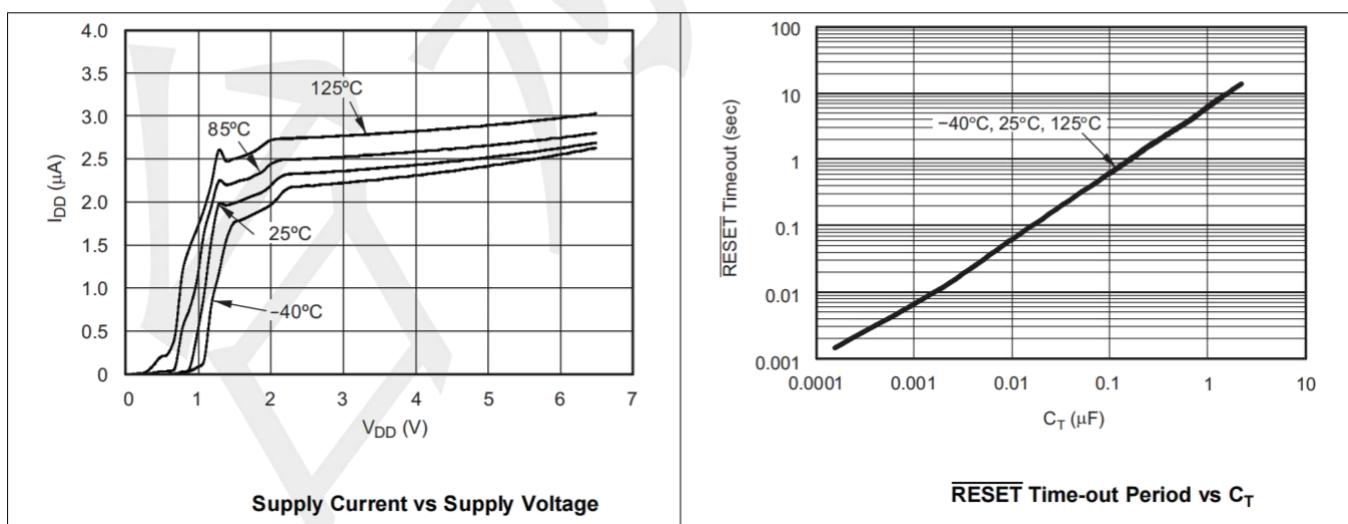

| $I_{DD}$                              | Supply current (into $V_{DD}$ pin)      | $V_{DD} = 3.3\text{V}$ , RESET not asserted, MR, RESET, $C_T$ open |                                                             |              | 2.8       | 5                  | $\mu\text{A}$ |  |

|                                       |                                         | $V_{DD} = 6.5\text{V}$ , RESET not asserted, MR, RESET, $C_T$ open |                                                             |              | 3.0       | 6                  |               |  |

| $V_{OL}$                              | Low-level output voltage                | $1.3\text{V} \leq V_{DD} < 1.8\text{V}$ , $I_{OL} = 0.4\text{mA}$  |                                                             |              |           | 0.3                | V             |  |

|                                       |                                         | $1.3\text{V} \leq V_{DD} \leq 6.5\text{V}$ , $I_{OL} = 1\text{mA}$ |                                                             |              |           | 0.4                | V             |  |

| Power-up reset voltage <sup>(1)</sup> |                                         | $V_{OL}$ (max) = 0.2 V, $I_{RESET} = 15\text{\mu A}$               |                                                             |              |           | 1.0                | V             |  |

| $V_{IT}$                              | Negative-going input threshold accuracy | TPAX3808G01                                                        |                                                             | -2           | $\pm 1$   | 2                  | %             |  |

|                                       |                                         | $V_{IT} \leq 3.3\text{V}$                                          |                                                             | -1.5         | $\pm 0.5$ | 1.5                |               |  |

|                                       |                                         | $3.3\text{V} < V_{IT} \leq 5\text{V}$                              |                                                             | -2           | $\pm 1$   | 2                  |               |  |

|                                       |                                         | $V_{IT} \leq 3.3\text{V}$                                          | $-40^{\circ}\text{C} < T_J < 85^{\circ}\text{C}$            | -1.25        | $\pm 0.5$ | 1.25               |               |  |

|                                       |                                         | $3.3\text{V} < V_{IT} \leq 5\text{V}$                              |                                                             | -1.5         | $\pm 0.5$ | 1.5                |               |  |

| $V_{HYS}$                             | Hysteresis on $V_{IT}$ pin              | TPAX3808G01                                                        |                                                             |              | 1.5       |                    | $\%V_{IT}$    |  |

|                                       |                                         | $-40^{\circ}\text{C} < T_J < 85^{\circ}\text{C}$                   |                                                             |              | 1         | 2                  |               |  |

| $R_{RM}$                              | MR internal pullup resistance           | $V_{SENSE} = V_{IT}$                                               |                                                             | 70           | 90        |                    | k $\Omega$    |  |

| $I_{SENSE}$                           | Input current at SENSE pin              | TPAX3808G01                                                        |                                                             | -25          |           | 25                 | nA            |  |

|                                       |                                         | $V_{SENSE} = 6.5\text{V}$                                          |                                                             |              | 1.7       |                    | $\mu\text{A}$ |  |

| $I_{OH}$                              | RESET leakage current                   | $V_{RESET} = 6.5\text{V}$ , RESET not asserted                     |                                                             |              |           | 300                | nA            |  |

| $C_{IN}$                              | Input capacitance, any pin              | $C_T$ pin                                                          | $V_{IN} = 0\text{V}$ to $V_{DD}$                            |              | 5         |                    | pF            |  |

|                                       |                                         | Other pins                                                         | $V_{IN} = 0\text{V}$ to $6.5\text{V}$                       |              | 5         |                    |               |  |

| $V_{IL}$                              | MR logic low input                      |                                                                    |                                                             | 0            |           | $0.3\text{V}_{DD}$ | V             |  |

| $V_{IH}$                              | MR logic high input                     |                                                                    |                                                             | 0.7 $V_{DD}$ |           | $V_{DD}$           | V             |  |

| $t_d$                                 | RESET delay time                        | $C_T = \text{Open}$                                                | See Timing Diagram                                          | 12           | 20        | 28                 | ms            |  |

|                                       |                                         | $C_T = V_{DD}$                                                     |                                                             | 180          | 300       | 420                |               |  |

|                                       |                                         | $C_T = 100\text{pF}$                                               |                                                             | 0.75         | 1.25      | 1.75               |               |  |

|                                       |                                         | $C_T = 180\text{nF}$                                               |                                                             | 0.7          | 1.2       | 1.7                |               |  |

| $t_{pHL}$                             | Propagation delay                       | MR to RESET                                                        | $V_{IH} = 0.7\text{V}_{DD}$ , $V_{IL} = 0.3\text{V}_{DD}$   |              | 150       |                    | nS            |  |

|                                       | High-level to low-level RESET delay     | SENSE to RESET                                                     | $V_{IH} = 1.05\text{V}_{IT}$ , $V_{IL} = 0.95\text{V}_{IT}$ |              | 20        |                    | uS            |  |

| $t_w$                                 | Maximum transient duration              | SENSE                                                              | $V_{IH} = 1.05\text{V}_{IT}$ , $V_{IL} = 0.95\text{V}_{IT}$ |              | 20        |                    | uS            |  |

|                                       |                                         | MR                                                                 | $V_{IH} = 0.7\text{V}_{DD}$ , $V_{IL} = 0.3\text{V}_{DD}$   |              | 0.001     |                    | uS            |  |

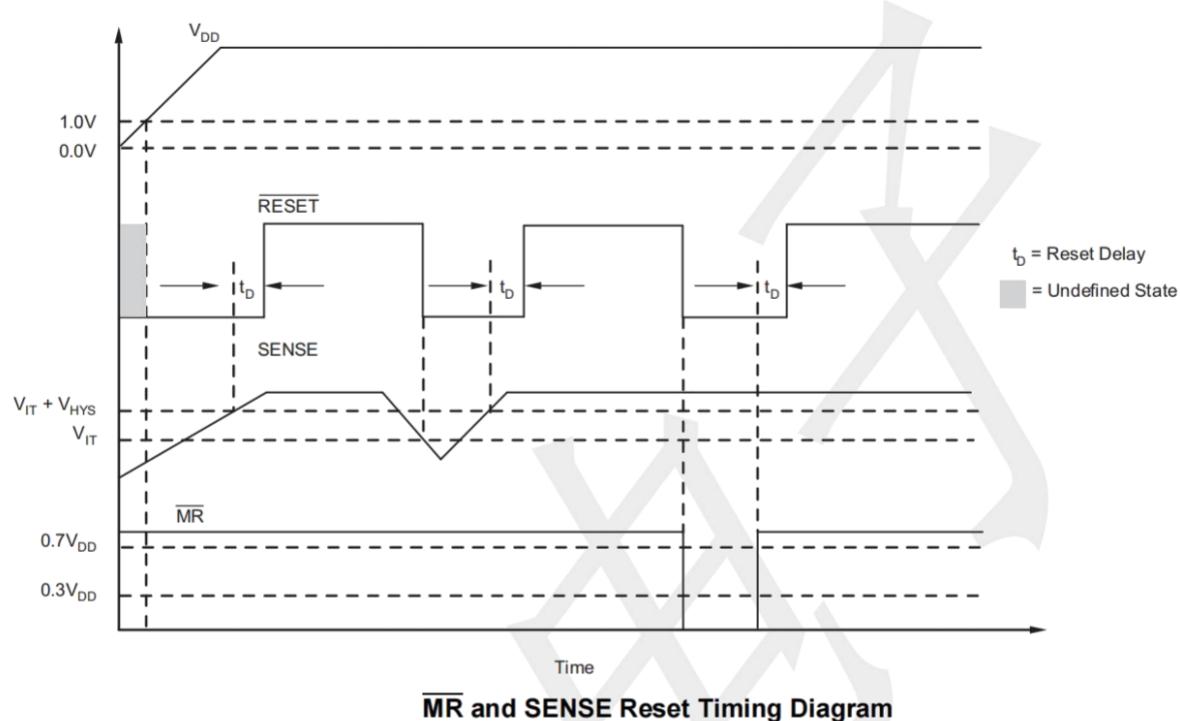

## Timing Diagram

**Truth Table**

| $\overline{MR}$ | $SENSE > V_{IT}$ | $\overline{RESET}$ |

|-----------------|------------------|--------------------|

| L               | 0                | L                  |

| L               | 1                | L                  |

| H               | 0                | L                  |

| H               | 1                | H                  |

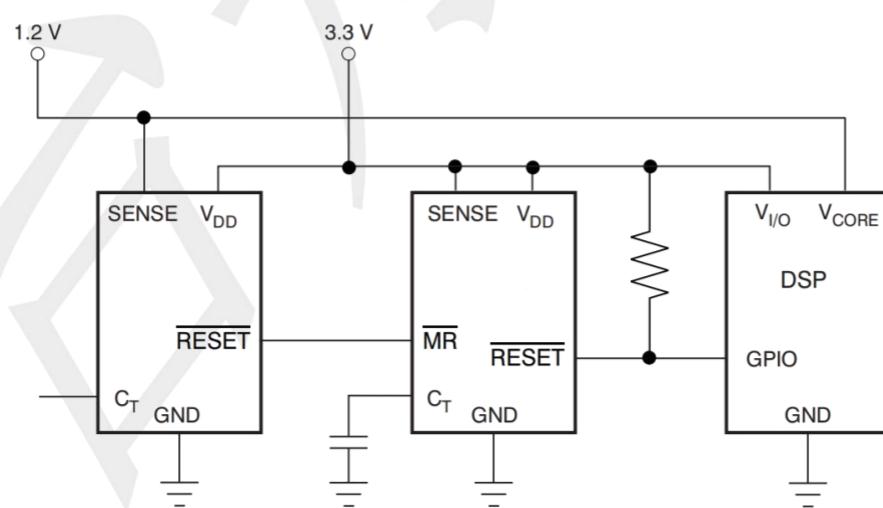

## Typical Application Schematic

## Functional Description

The microprocessor supervisory product family is designed to assert a RESET signal when either the SENSE pin voltage drops below  $V_{IT}$  or the manual reset ( MR ) is driven low. The RESET output remains asserted for a user-adjustable time after both the manual reset ( MR ) and SENSE voltages return above the respective thresholds. A broad range of the voltage threshold and reset delay time adjustments are available, allowing these devices to be used in a wide array of applications. Reset threshold voltages can be factory-set from 0.82V to 3.3V or from 4.4V to 5.0V, while the can be set to any voltage above 0.405V using an external resistor divider. Two preset delay times are also user-selectable: connecting the  $C_T$  pin to  $V_{DD}$  results in a 300ms reset delay, while leaving the  $C_T$  pin open yields a 20ms reset delay. In addition, connecting a capacitor between  $C_T$  and GND allows the designer to select any reset delay period from 1.25ms to 10s.

## RESET Output

The open-drain RESET output is typically connected to the RESET input of a microprocessor. A pull-up resistor must be used to hold this line high when RESET is not asserted. The RESET output is undefined for voltage below 1.0V, but this is normally not a problem since most microprocessors do not function below this voltage. RESET remains high (unasserted) as long as SENSE is above its threshold( $V_{IT}$ ) and the manual reset ( MR ) is logic high. If either SENSE falls below  $V_{IT}$  or MR is driven low, RESET is asserted, driving the RESET pin to low impedance.

Once MR is again logic high and SENSE is above  $V_{IT} + VHYS$  (the threshold hysteresis), a delay circuit is enabled which holds RESET low for a specified reset delay period. Once the reset delay has expired, the RESET pin goes to a high impedance state. The pull-up resistor from the open-drain RESET to the supply line can be used to allow the reset signal for the microprocessor to have a voltage higher than  $V_{DD}$  (up to 6.5V). The pull-up resistor should be no smaller than 10k $\Omega$  as a result of the finite impedance of the RESET line.

## SENSE Input

The SENSE input provides a pin at which any system voltage can be monitored. If the voltage on this pin drops below  $V_{IT}$ , then RESET is asserted. The comparator has a built-in hysteresis to ensure smooth RESET assertions and de-assertions. It is good analog design practice to put a 1nF to 10nF bypass capacitor on the SENSE input to reduce sensitivity to transients and layout parasitic. The can be used to monitor any voltage rail down to 0.405V by resister divider.

## Manual Reset ( MR ) Input

The manual reset ( MR ) input allows a processor or other logic circuits to initiate a reset. A logic low (0.3V $_{DD}$ ) on MR will cause RESET to assert. After MR returns to a logic high and SENSE is above its reset threshold, RESET is de-asserted after the user defined reset delay expires. Note that MR is internally tied to  $V_{DD}$  using a 90kohm resistor so this pin can be left unconnected if MR will not be used. Do not apply voltage level over VDD.

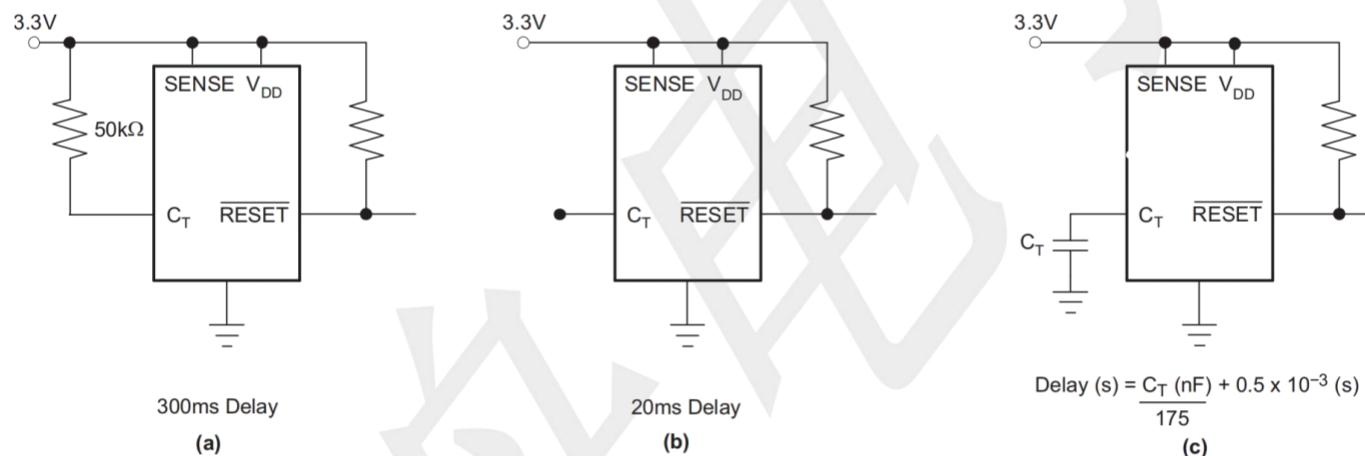

## Selecting the RESET Delay Time

The has three options for setting the RESET delay time.

1. A fixed 300ms typical delay time by tying  $C_T$  to  $V_{DD}$  through a resistor from  $40k\Omega$  to  $200k\Omega$ . As below Figure (a) shown.

2. A fixed 20ms delay time by leaving the  $C_T$  pin open. As below Figure (b) shown.

3. A ground referenced capacitor connected to  $C_T$  for a user-defined program time between 1.25ms and 10s. The capacitor  $C_T$  should be  $\geq 100pF$  nominal value in order for the to recognize that the capacitor is present. The capacitor value for a given delay time can be calculated using the following equation:  $C_T(nF) = [t_D(s) - 0.5 \times 10^{-3}(s)] \times 175$ . As below Figure (c) shown.

The reset delay time is determined by the time it takes an on-chip precision 220nA current source to charge the external capacitor to 1.23V. When a RESET is asserted the capacitor is discharged. When the RESET conditions are cleared, the internal current source is enabled and begins to charge the external capacitor. When the voltage on this capacitor reaches 1.23V, RESET is de-asserted. Note that a low leakage type capacitor such as a ceramic should be used and the stray capacitance around this pin may cause errors in the reset delay time.

Configuration Used to Set the RESET Delay Time

## Application Curves

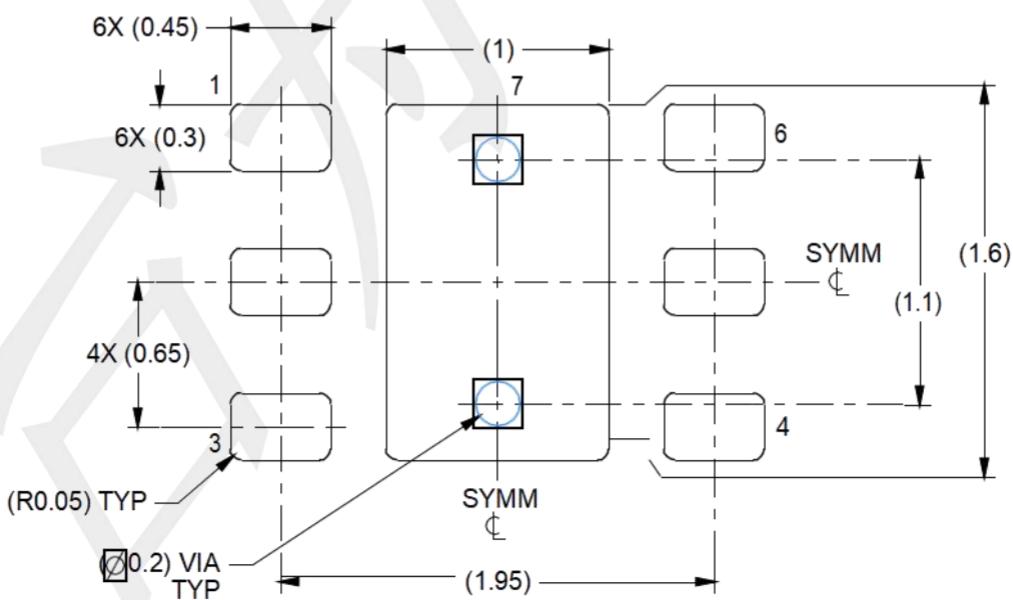

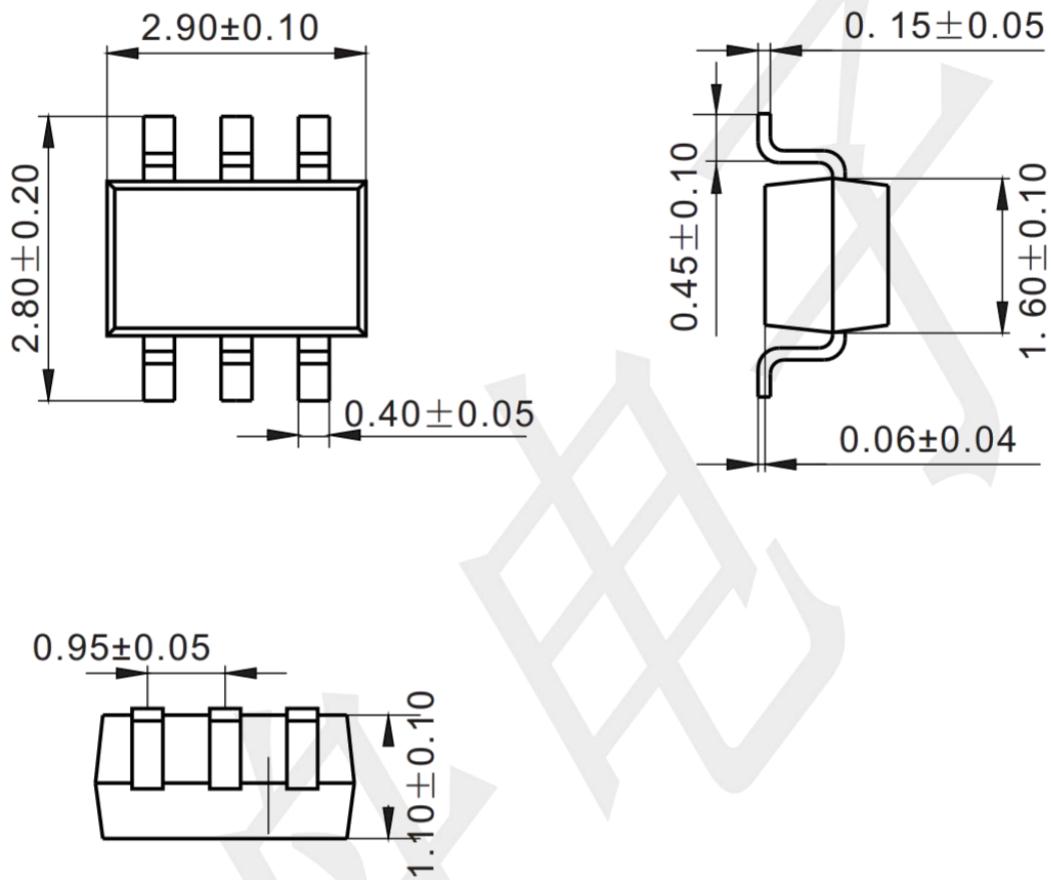

**Package Outline Dimensions (unit: mm)**

SOT23-6L

**Mounting Pad Layout (unit: mm)**

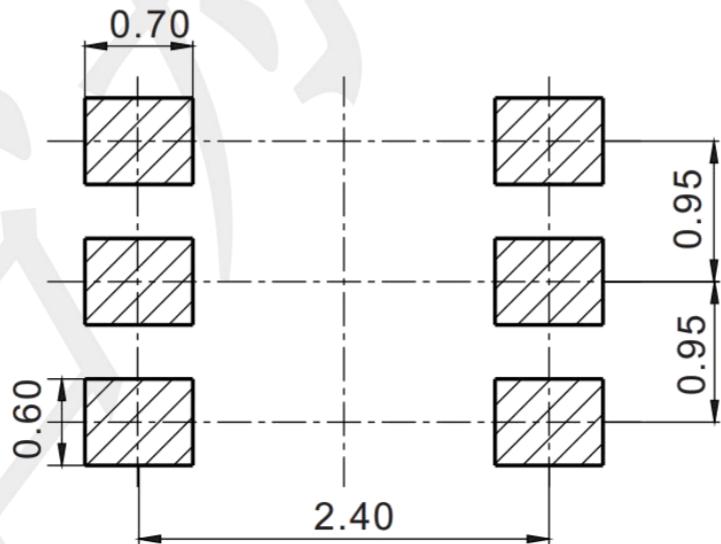

### Package Outline Dimensions (unit: mm)

DFN2X2-6L

### Mounting Pad Layout (unit: mm)